# Arm® Cortex®-M35P r1p1 Lite Security Target

Version 1.1

## Cortex®-M35P

#### **Lite Security Target**

Copyright © 2019, 2020 Arm Limited (or its affiliates). All rights reserved.

#### **Release Information**

#### **Document History**

| Version | Date             | Confidentiality  | Change                 |

|---------|------------------|------------------|------------------------|

| 1.0     | 15 November 2019 | Non-Confidential | First draft for r1p1   |

| 1.1     | 16 January 2020  | Non-Confidential | First release for r1p1 |

## **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ° or ™ are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="http://www.arm.com/company/policies/trademarks">http://www.arm.com/company/policies/trademarks</a>.

Copyright  $^{\circ}$  2019, 2020 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

## **Web Address**

http://www.arm.com

# **Contents**

| 1 About this document                             | 6  |

|---------------------------------------------------|----|

| 1.1. Scope                                        | 6  |

| 1.2. References                                   | 6  |

| 1.3. Terms and Abbreviations                      | 6  |

| 1.4. Glossary                                     | 8  |

| 1.5. Typographical conventions                    | 8  |

| 2 Introduction                                    | 9  |

| 2.1. ST reference                                 | 9  |

| 2.2. TOE reference                                | 9  |

| 2.3. TOE overview                                 | 9  |

| 2.4. TOE identification                           | 10 |

| 2.5. TOE description                              | 10 |

| 2.5.1 TOE logical scope                           | 10 |

| 2.5.2 Physical scope                              | 16 |

| 2.6. TOE lifecycle and delivery                   | 16 |

| 2.7. Configuration                                | 18 |

| 3 Conformance claims                              | 19 |

| 3.1. CC conformance claims                        | 19 |

| 3.2. PP claim                                     | 19 |

| 3.3. Package claim                                | 19 |

| 3.4. Conformance claim rationale                  | 19 |

| 4 Security problem definition                     | 20 |

| 4.1. Core SPD and additional SPD                  | 20 |

| 4.2. Description of assets                        | 21 |

| 4.3. Core SPD                                     | 21 |

| 4.3.1 Core threats                                | 21 |

| 4.3.2 Core organisational security policies       | 21 |

| 4.3.3 Core assumptions                            | 22 |

| 4.4. Additional SPD                               | 22 |

| 4.4.1 Additional threats                          | 22 |

| 4.4.2 Additional organisational security policies | 22 |

| 4.4.3 Additional assumptions                      | 23 |

| 5 Security objectives                             | 24 |

| 5.1. Core security objectives                            | 24  |

|----------------------------------------------------------|-----|

| 5.1.1 Core security objectives for the environment       | 24  |

| 5.1.2 Core security objectives for the TOE               | 24  |

| 5.1.3 Core security objective rationale                  | 25  |

| 5.2. Additional security objectives                      | 26  |

| 5.2.1 Additional security objectives for the environment | 26  |

| 5.2.2 Additional security objectives for the TOE         | 26  |

| 5.2.3 Additional security objective rationale            | 27  |

| 6 Extended components definition                         | 28  |

| 7 Security requirements                                  | 29  |

| 7.1. Typographical conventions                           | 29  |

| 7.2. Core SFRs                                           | 29  |

| 7.3. SFRs for the MPU Extension                          | 29  |

| 7.3.1 Memory access protection                           | 30  |

| 7.3.2 Security functional requirements                   | 32  |

| 7.4. SFRs for the Security Extension                     | 35  |

| 7.4.1 SE access control                                  | 35  |

| 7.4.2 Access control definition                          | 36  |

| 7.4.3 Security functional requirements                   | 40  |

| 7.5. Security assurance requirements                     | 42  |

| 7.5.1 Refinements of the TOE assurance requirements      | 44  |

| 7.6. Security requirements rationale                     | 45  |

| 7.6.1 Rationale for the security functional requirements | 45  |

| 7.6.2 Dependencies of security functional requirements   | 48  |

| 7.6.3 Rationale for the assurance requirements           | 49  |

| 7.6.4 Dependencies of security assurance requirements    | 49  |

| 7.6.5 Security requirements are internally consistent    | 50  |

| 8 TOE summary specification                              | 51  |

| 8.1. Security functions                                  | 51  |

| 8.1.1 SF.Leak.Prot - Leakage protection                  | 51  |

| 8.1.2 SF.Malfunction - Malfunction protection            | 51  |

| 8.1.3 SF.MPU - MPU access control                        | 52  |

| 8.1.4 SF.SE – SE access control                          | 52  |

| 8.1.5 SF.SE uses SF.MPU                                  | 54  |

| 8.2. Protection against tampering and bypass             | 56  |

| 8.2.1 SM.Log-Tamper-Protect                              | 56  |

| 8.2.2 SM Rynass-Protect                                  | 5.0 |

# 1 About this document

# **1.1. Scope**

This document identifies the security properties of the TOE and defines the scope of the evaluation.

## 1.2. References

This document refers to the following publications:

| Document   | Title                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| [PP84]     | Security IC Platform Protection Profile with Augmentation Packages, BSI-CC-PP-0084-2014, version 1.0, date 3.01.2014                                    |

|            | Common Criteria for Information Technology Security Evaluation - Part 1: Security assurance components, CCMB-2017-04-001, Version 3.1 Rev 5, April 2017 |

| [CC]       | Common Criteria for Information Technology Security Evaluation - Part 2: Security assurance components, CCMB-2017-04-002, Version 3.1 Rev 5, April 2017 |

|            | Common Criteria for Information Technology Security Evaluation - Part 3: Security assurance components, CCMB-2017-04-003, Version 3.1 Rev 5, April 2017 |

|            | Common Criteria for Information Technology Security Evaluation — Evaluation methodology, CCMB-<br>2017-04-0004, Version 3.1 Rev 5, April 2017           |

| [TRM]      | Arm® Cortex®-M35P Processor Technical Reference Manual (100883)                                                                                         |

| [IIM]      | Arm® Cortex®-M35P Processor Integration and Implementation Manual (100886)                                                                              |

| [UGRM]     | Arm® Cortex®-M35P Processor User Guide Reference Manual (100887)                                                                                        |

| [PEN]      | Arm® Cortex®-M35P Product Errata Notice (AT627-DC-11000)                                                                                                |

| [RN]       | Arm® Cortex®-M35P Processor Release Note (PJDOC-466751330-5402)                                                                                         |

| [ArchSupp] | Arm® Cortex®-M35P v8-M Architecture Supplement (PJDOC-466751330-1229)                                                                                   |

| [Arm ARM]  | Arm®v8-M Architecture Reference Manual (DDI0553A.i)                                                                                                     |

## 1.3. Terms and Abbreviations

This document uses the following terms and abbreviations:

| Term or abbreviation | Meaning                                                                      |

|----------------------|------------------------------------------------------------------------------|

| АНВ                  | AMBA High-performance Bus                                                    |

| Armv8-M              | Armv8-M architecture described in the Arm®v8-M Architecture Reference Manual |

| BPU                  | Breakpoint Unit                                                              |

| С-АНВ                | Code AHB                                                                     |

| CC        | Common Criteria                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| CTI       | Cross-Trigger Interface                                                                                                                   |

| CoreSight | Arm on-chip debug and trace components, that provide the infrastructure for monitoring, tracing, and debugging a complete system on chip. |

| D-AHB     | Debug AHB                                                                                                                                 |

| DAP       | Debug Access Port                                                                                                                         |

| DMA       | Direct Memory Access                                                                                                                      |

| DSP       | Digital Signal Processing                                                                                                                 |

| DWT       | Data Watchpoint and Trace                                                                                                                 |

| EAL       | Evaluation Assurance Level                                                                                                                |

| EPPB      | External Private Peripheral Bus                                                                                                           |

| ETM       | Embedded Trace Macrocell                                                                                                                  |

| IC        | Integrated Circuit                                                                                                                        |

| IDAU      | Implementation Defined Attribution Unit                                                                                                   |

| IRQ       | Interrupt Request                                                                                                                         |

| ISR       | Interrupt Service Routine                                                                                                                 |

| ITM       | Instruction Trace Macrocell                                                                                                               |

| FPU       | Floating Point Unit                                                                                                                       |

| GPIO      | General Purpose Input/Output                                                                                                              |

| MPU       | Memory Protection Unit                                                                                                                    |

| MTB       | Micro Trace Buffer                                                                                                                        |

| NIC       | Network Interconnect                                                                                                                      |

| NVIC      | Nested Vectored Interrupt Controller                                                                                                      |

| PC        | Program Counter                                                                                                                           |

| PMSA      | Protected Memory System Architecture                                                                                                      |

| PP        | Protection Profile                                                                                                                        |

| S-AHB     | System AHB                                                                                                                                |

| SAR       | Security Assurance Requirement                                                                                                            |

| SAU       | Security Attribution Unit                                                                                                                 |

| SCS       | Secure Control Space                                                                                                                      |

| SE        | Armv8-M Security Extension                                                                                                                |

| SFR       | Security Functional Requirement                                                                                                           |

| SPD       | Security Problem Definition                                                                                                               |

| SPM       | Security Policy Model                                                                                                                     |

| ST   | Security Target              |

|------|------------------------------|

| SWO  | Serial Wire Output           |

| TOE  | Target of Evaluation         |

| TPA  | Trace Port Analyzer          |

| TPIU | Trace Port Interface Unit    |

| PPB  | Private Peripheral Bus       |

| WIC  | Wake-up Interrupt Controller |

# 1.4. Glossary

See the Arm glossary http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

# 1.5. Typographical conventions

This ST refers to [PP84] and [CC], as mentioned in **References** and therefore cites content directly copied from these references. In this ST, the original text copied from these references is typed as indicated here.

# 2 Introduction

### 2.1. ST reference

This ST is entitled Arm® Cortex®-M35P r1p1 Lite Security Target. The document version is 1.1 and dated 01/16/2020.

### 2.2. TOE reference

The TOE is identified as Cortex-M35P r1p1. It corresponds exactly to the components described in Table 1 TOE physical scope.

#### 2.3. TOE overview

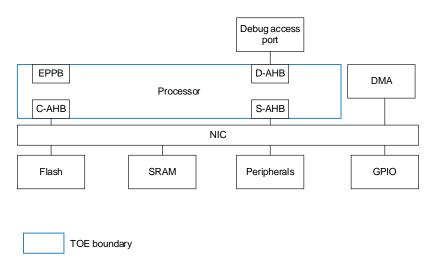

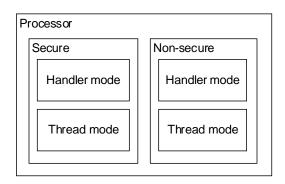

The TOE is the set of functionalities for a processor in a Security microcontroller IC. In this document, the TOE is also referred to as *the processor*. The intended environment for the TOE is the Security IC for smart card applications or similar services as identified and described in [PP84]. The TOE provides the functionality for software execution and controlling access to memory addresses in a Security IC.

The following figure shows a simplified general architecture of a Security IC microcontroller with the TOE processor part indicated and the major interfaces to the surrounding Security IC components.

Figure 1 TOE component of a Security IC

The user of the TOE is the designer of a Security IC microcontroller product that integrates the TOE into their design for the microcontroller product. In this document, this user is referred to as the IC Designer. The user of the TOE is also the programmer of the Security IC dedicated software and the programmer of the Security IC embedded software that use the TOE programming interfaces consisting of the TOE instruction set and exception handling. It is the responsibility of the IC designer to instruct the programmer how to use the TOE.

The TOE is delivered as source code to be integrated by the IC Designer into the source code of their Security microcontroller product. To this end, the TOE has several interfaces that facilitate integration:

Code AHB (C-AHB) interface.

- Version 1.1

- The C-AHB interface is used for any instruction fetch and data access to the Code region of the Armv8-M memory map.

- System AHB (S-AHB) interface.

- The S-AHB interface is used for any instruction fetch and data access to the memory-mapped SRAM, Peripheral, External RAM and External device, or Vendor SYS regions of the Armv8-M memory map.

- External PPB (EPPB) interface.

- The EPPB interface enables access to TOE external debug and trace components in a system connected to the processor.

- Debug AHB (D-AHB) interface.

- The D-AHB slave interface allows a TOE external debugger access to registers, memory, and peripherals. The D-AHB interface provides debug access to the processor and the complete memory map.

See the **TOE logical scope** section for more information on these interfaces.

The TOE is compliant with the Armv8-M mainline architecture described in the Arm®v8-M Architecture Reference Manual. The Armv8-M mainline architecture is adaptable and enables a customer to tailor the functionality of the processor in their IC design from what are called architecture extensions. The following architecture extensions are available in the Cortex-M35P processor:

- The MPU Extension, which adds memory access control functionality.

- The Security Extension (SE), which adds security management. This extension can be referred to as Arm® TrustZone® for the TOE and requires the MPU Extension to be included.

- The floating-point (FPU) Extension.

- The Digital Signal Processing (DSP) Extension.

- The Debug Extension, which includes a debugger component that can be used for testing purposes during IC manufacturing.

The IC Designer chooses to include or exclude these extensions in their processor implementation using configuration parameters as part of the processor integration process, which is the first step they undertake after the delivery of the TOE to integrate the TOE in their IC design.

#### 2.4. TOE identification

The TOE is the Cortex-M35P r1p1 product. Cortex-M35P r1p1 identifies the TOE including its components and guidance documentation listed in the **Physical scope** section. r1p1 is the version of the evaluated product where r is the major revision of the product (variant) and p is the minor revision of the product (revision). This version is identified in the *Arm® Cortex®-M35P Processor Release Note*. Any change in the TOE components or guidance documentation leads to a new version of the evaluated product, thus a new TOE.

## 2.5. TOE description

## 2.5.1 TOE logical scope

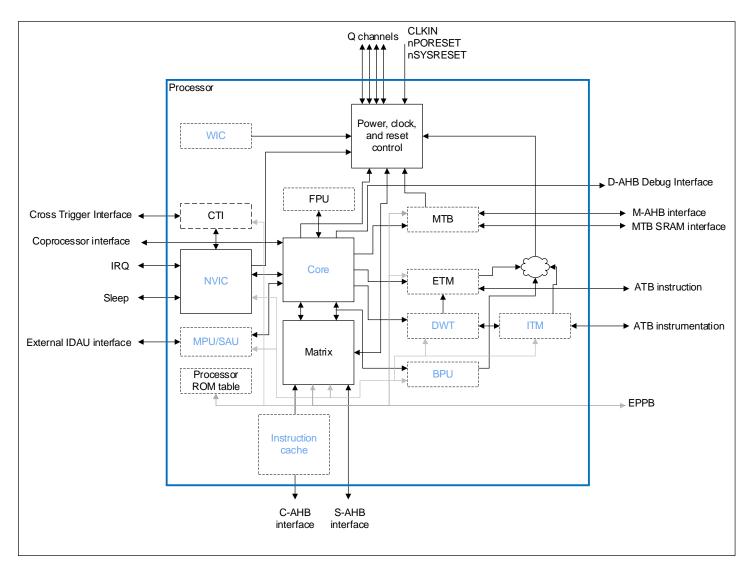

The following figure shows the TOE logical scope by identifying the logical components of the processor and the interfaces to the TOE environment.

TOE boundary

Figure 2 TOE logical scope

This figure shows the main interfaces identified in **Figure 1 TOE component of a Security IC** and details other interfaces. Components marked with dotted lines are optional as they are part of architecture extensions.

Although the MPU is part of the MPU extension and therefore can be optionally included or excluded during processor integration, it should always be included for a certified configuration.

Components in blue are configurable during processor integration. For example, the number of programmable memory regions in the MPU and SAU can be configured during processor integration.

The following subsections give an overview of the logical scope for each component.

#### **Processor core**

The processor core provides:

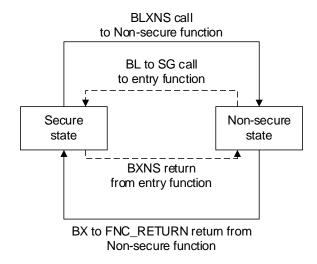

- Full support for the Armv8-M Security Extension.

- Harvard 32-bit AHB bus interfaces with vector fetch capability on the instruction side.

- 2/3 stage pipeline with early completion of common arithmetic instructions.

- Single-cycle branch latency.

- Limited dual-issue of common 16-bit instruction pairs.

- Single cycle 32×32-bit multiplier with two-cycle result latency for MAC operations.

- Integer divide unit with support for operand-dependent early termination.

- Support for interrupted continuable load and store multiple operations.

- Load and store operations both support precise errors.

#### Instruction cache

The instruction cache has the following features:

- 2-way set associative.

- 16-byte cache lines.

- Configurable size of 2KB, 4KB, 8KB, or 16KB.

- One-cycle penalty on uncacheable transactions.

- Read transactions are subject to caching and write transactions invalidate the cache.

## Security attribution and memory protection (SAU/MPU)

The Cortex-M35P processor supports the Armv8-M PMSA that provides programmable support for memory protection using software controllable regions.

Memory regions can be programmed to generate faults when they are inappropriately accessed by unprivileged software, reducing the scope of incorrectly written application code. The architecture includes fault status registers to allow an exception handler to determine the source of the fault and to apply corrective action or notify the system.

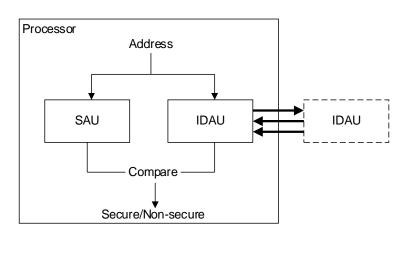

The Cortex-M35P processor also includes optional support for defining memory regions as Secure or Non-secure, as defined in the Armv8–M Security Extension, and protecting the regions from accesses with an inappropriate level of security.

## Floating Point Unit (FPU)

The FPU provides:

- Instructions for single-precision (C programming language float type) data-processing operations.

- Instructions for double-precision (C double type) load and store operations.

- Combined multiply-add instructions for increased precision (Fused MAC).

- Hardware support for conversion, addition, subtraction, multiplication with optional accumulate, division, and square-root.

- Hardware support for denormals and all IEEE Standard 754-2008 rounding modes.

- 32×32-bit single-precision registers or 16×64-bit double-precision registers.

- Lazy floating-point context save. Automated stacking of floating-point state is delayed until ISR attempts to execute a floating-point instruction. This reduces the latency to enter the ISR and removes floating-point context save for ISRs that do not use floating-point.

#### **Nested Vectored Interrupt Controller (NVIC)**

The NVIC is closely integrated with the core to achieve low-latency interrupt processing.

Functions of the NVIC include:

- External interrupts, configurable from 1 to 480 using a contiguous or non-contiguous mapping. This is configured at implementation.

- Configurable levels of interrupt priority from 8 to 256. This is configured at implementation.

- Dynamic reprioritisation of interrupts.

- Priority grouping. This enables selection of preempting interrupt levels and non-preempting interrupt levels.

- Support for tail-chaining and late arrival of interrupts. This enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Optional support for the Armv8-M Security Extension. Secure interrupts can be prioritized above any Non-secure interrupt.

## Wake-up Interrupt Controller (WIC)

The optional WIC supports the powering down of the core for power saving purposes. The WIC is responsible for registering pending exceptions and detecting wakeup conditions.

#### Power, clock, and reset control

The power, clock, and reset control is responsible for interfacing with an external PMU and generating the main clocks and resets for each power domain.

### **Cross Trigger Interface Unit (CTI)**

The optional CTI enables the debug logic, MTB, and ETM to interact with each other and with other CoreSight components.

## **Embedded Trace Macrocell (ETM)**

The optional ETM provides instruction-only capabilities when configured.

## Micro Trace Buffer (MTB)

The MTB provides a simple low-cost execution trace solution for the Cortex-M35P processor.

Trace is written to an SRAM interface, and can be extracted using a dedicated AHB slave interface on the processor, MTB AHB. The MTB can be controlled by memory mapped registers in the PPB region or by events generated by the DWT or through the CTI.

#### Debug and trace additional components

Debug and trace components include:

- A configurable Breakpoint Unit (BPU) that implements a configurable number of comparators for breakpoints generation.

- A configurable Data Watchpoint and Trace unit (DWT) that implements watchpoints, data tracing, and system profiling.

- An Instruction Trace Macrocell (ITM) that creates a printf() style debug trace.

- A ROM table that allows debuggers to discover the list of debug components included in the Cortex-M35P processor.

### **Matrix**

The matrix is a multilayer interconnect that routes the memory access requested by the core to the selected destination such as the C-AHB, S-AHB, EPPB, or internal PPB registers. Port selection is done according to the transaction address.

#### **Interfaces**

#### **C-AHB and S-AHB**

The C-AHB and S-AHB ports implement the AMBA5 AHB protocol and connect the core to external memories. These ports are physically driven by the matrix, and C-AHB can also be driven by the instruction cache if present. In a typical implementation, C-AHB connects to flash memories and S-AHB is dedicated to SRAMs.

#### **External IDAU interfaces**

The TOE includes support for an external attribution unit to allow the security level associated with a given address to be defined by the system. The output of this port is the address that need to be checked, and the input is the security information provided by the external attribution unit.

#### Sleep

Thanks to this interface, the TOE shares its power state with the external system. When the core enters a low-power state, it uses this port to communicate this information and the type of sleep it has entered (SLEEPING or DEEPSLEEP).

#### **IRQ**

This port collects all the external interrupts that are forwarded to the NVIC which is responsible for prioritizing and treating the interrupts. The TOE can support up to 480 external interrupts.

#### **Coprocessor interface**

The external Coprocessor interface allows the integration of tightly coupled hardware accelerators. The TOE accesses this interface using the architectural coprocessor instructions. This interface supports up to eight separate coprocessors. The system can configure which coprocessors are included in Secure and Non-secure state.

#### **Q-Channels**

A Q-Channel is a low-power interface. It supports the handshake mechanism that allow an external power controller to request the entrance of a TOE power domain into a quiescent state. Each TOE power domain has its own Q-channel interface. Each power domain uses the interface to share internal activity when it has stopped and then enters a low-power state.

#### **Debug interface D-AHB**

The debug interface is an AMBA5 AHB slave port. It allows an external debugger agent to connect to the internal TOE resources. This includes:

- The registers in the system.

- The memory-mapped devices.

- The internal core registers when the core is halted.

- The debug control registers even when reset is asserted.

External memory can also be accessed.

#### **EPPB**

The EPPB is a 32-bit AMBA4 APB interface designed for integration with the Debug and trace components and ROM tables. It is used for data only accesses to the memory region  $0 \times E0040000 - 0 \times E00FFFFF$  and it is not intended for general peripheral usage.

#### ATB instrumentation and ATB instruction

These two ports implement the AMBA4 ATB interface protocol which is a used by trace components to pass format-independent trace data through a CoreSight system. These ports are driven by the ITM and ETM respectively.

#### MTB SRAM interface and M-AHB interface

MTB SRAM interface is a dedicated port driven by the MTB which generates the execution trace to be written in the MTB SRAM. The M-AHB is an AMBA5 AHB slave port that allows reading the content of the SRAM passing through the MTB.

## **Cross Trigger Interface**

The Cross Trigger Interface is a standard interface that enables the core debug logic and ETM and MTB to interact with each other and with additional CoreSight debug and trace components in the system external to the TOE.

## **Countermeasures**

In addition, the TOE includes features that protect against information leakage and malfunction.

# 2.5.2 Physical scope

The following table lists the set of hardware, software, and document components that are delivered.

| Component                                                         | Туре                    | Version                    |

|-------------------------------------------------------------------|-------------------------|----------------------------|

| Cortex-M35P Synthesizable Verilog                                 | Verilog code (.v files) | AT627-MN-22110-r1p1-00rel0 |

| Cortex-M35P Execution Test Bench                                  | Testbench (C code)      | AT627-MN-22010-r1p1-00rel0 |

| Cortex-M35P Functional Test Source                                | Testbench (C code)      | AT627-VE-70006-r1p1-00rel0 |

| Cortex-M35P RAM Integration Test Bench                            | Testbench (C code)      | AT627-MN-70002-r1p1-00rel0 |

| Arm® Cortex®-M35P Product Errata Notice                           | Document (.pdf)         | AT627-DC-11000-r1p1-00rel0 |

| Arm® Cortex®-M35P Release Note                                    | Document (.pdf)         | AT627-DC-06003-r1p1-00rel0 |

| Arm® Cortex®-M35P Processor Technical Reference Manual            | Document (.pdf)         | AT627-DA-03001-r1p1-00rel0 |

| Arm® Cortex®-M35P Processor Integration and Implementation Manual | Document (.pdf)         | AT627-DC-70047-r1p1-00rel0 |

| Arm® Cortex®-M35P Processor User Guide Reference Manual           | Document (.pdf)         | AT627-DA-03005-r1p1-00rel0 |

| Arm® Cortex®-M35P v8-M Architecture Supplement                    | Document (.pdf)         | AT627-DC-50000-r1p1-00rel0 |

| Arm® Cortex®-M35P r1p1 Security Guidance                          | Document (.pdf)         | PJDOC-466751330-8802 3.1   |

Table 1 TOE physical scope

### Note:

All documents are restricted by nature. Access to these documents depends on your agreement with Arm.

# 2.6. TOE lifecycle and delivery

This ST claims a part of Protection Profile [PP84]. The following figure shows the lifecycle for composite products based on a Security IC as described in [PP84]. The development of the TOE covers a part of Phase 2. The delivery of the TOE takes place halfway Phase 2.

IC embedded software development

Phase 2:

IC development

Phase 3:

IC manufacturing

Phase 4:

IC packaging

Phase 5:

Composite product integration

Phase 1:

Phase 6: Personalization

Phase 7: Operational usage

Figure 3 Lifecycle according to [PP84]

After delivery of the TOE source code to customers, the IC designer starts integrating the TOE into their IC design in the middle of Phase 2.

# 2.7. Configuration

The Cortex-M35P processor is configurable. As part of the integration process, the IC designer can decide to include or exclude optional extensions identified in the **TOE overview** section. The IC designer can also choose the size of configurable countermeasures (see the **TOE summary specification** chapter for details on configuration of countermeasures). After configuration, the identity of the TOE is determined by the source code version and the set of configuration parameters used. This identity is assessed during the sign-off process, which is based on log files that result from the configuration process.

# 3 Conformance claims

### 3.1. CC conformance claims

This document claims to be conformant to the CC version 3.1. Furthermore, it claims to be conformant to the CC Part 2 and conformant to the CC Part 3.

This document has been built with the *Common Criteria for Information Technology Security Evaluation; Version 3.1* which comprises:

- Common Criteria, Part 1: Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and General Model, Version 3.1, Revision 5, April 2017.

- Common Criteria, Part 2: Common Criteria for Information Technology Security Evaluation, Part 2: Security Functional Components, Version 3.1, Revision 5, April 2017.

- Common Criteria, Part 3: Common Criteria for Information Technology Security Evaluation, Part 3: Security Assurance Components, Version 3.1, Revision 5, April 2017.

- Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1, Revision 5, April 2017.

### 3.2. PP claim

This ST does not claim conformance to a PP. This ST claims a subset of the Security Problem Definition and the Security Requirements of the IC Platform Protection Profile [PP84].

The purpose of this document is to enable the Designer of Security IC products to certify their product from a composite evaluation, in which the certification results of this TOE can be reused. To this end, the [PP84] objectives that are not implemented in the TOE have been claimed as objectives for the environment of the TOE.

# 3.3. Package claim

This ST claims conformance to the assurance package EAL6 augmented with ASE TSS.2 and ALC FLR.1.

### 3.4. Conformance claim rationale

The purpose of this ST is to provide a platform certificate to a composite evaluation for a Security microcontroller claiming [PP84]. The EAL of [PP84] is EAL4 augmented with the assurance components ALC\_DVS.2 and AVA\_VAN.5. The assurance claim of this ST includes all assurance components of [PP84].

By claiming EAL6, this ST can provide a base component for Security IC evaluations claiming conformance to [PP84], up to and including EAL6.

By claiming ASE\_TSS.2, this ST also explains as part of the summary specification how the TOE protects itself against bypass and tampering.

By claiming ALC\_FLR.1, this ST also explains how Arm protects the TOE and corporate information.

#### Version 1.1

# 4 Security problem definition

#### 4.1. Core SPD and additional SPD

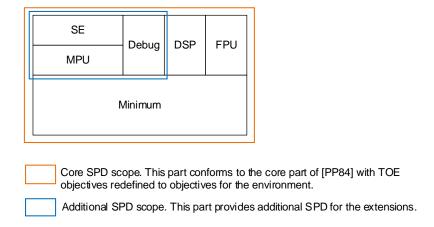

The **PP claim** section explains that the purpose of this ST is to provide a base part to a composite evaluation for a Security IC that claims conformance to [PP84]. The intention of this ST is also to help the Security IC designer claim the security for their IC product, in line with the choices that the configuration process allows. To this end, the SPD in this ST has a core part which defines the security problem for all possible processor configurations resulting from the configuration process, and additional SPDs for the services that the extensions provide. The following figure shows the scope of the different parts in the SPD.

Figure 4 Core and additional SPD

This figure shows that the SE depends on both the services of the MPU Extension and the minimum functionality. The other extensions are only dependent on the minimum functionality.

The core part of the SPD is according to the core part of [PP84], through which some TOE objectives have been redefined to objectives for the environment. The SPD description for the extensions add threats, organisational security policies, assumptions, and objectives specific to the extensions. The ST for the user Security IC claims compliance to [PP84] and additionally claims threats, organisational security policies, assumptions, and objectives for the extensions that remain in the design of the Security IC after TOE configuration.

There is a distinction between additional SPD and optional extensions. Additional SPDs are SPDs in addition to the [PP84]. These additional SPDs map to functional extensions of the TOE architecture that can be optionally included or excluded during the customer integration process. However, to have a meaningful TOE configuration as basis for certification the MPU extension must be included as a minimum during the integration process.

After delivery of the TOE, the customer ST for the user Security IC will claim compliance to [PP84] and additionally will claim SPD (threats, organisational security policies, assumptions, and objectives) for the extensions that remain in the design of the Security IC after TOE integration.

## 4.2. Description of assets

The assets to be protected are the end-user software and data in the external memories, which are known in [PP84] as IC dedicated software and embedded software. The TOE shall protect the confidentiality and integrity of the end-user data and software when it is transported to the TOE and when being processed by the core.

#### 4.3. Core SPD

The core of the SPDs describes the security problem to be solved for all TOE configurations after the user configuration process. This core SPD is according to a subset of the [PP84] SPD.

### 4.3.1 Core threats

Because the TOE is regarded a component of a Security IC, all threats defined in *Section 3.2* of [PP84] are regarded applicable to the TOE, except T.RND. [PP84] considers T.RND as a threat for a security service required in a Security microcontroller. Because this security service is not provided by the TOE, it is regarded not applicable for the TOE.

The following table shows the threats of [PP84] that are applicable to the TOE.

| Threat name         | Threat definition                       |

|---------------------|-----------------------------------------|

| T.Leak-Inherent     | Inherent Information Leakage            |

| T.Phys-Probing      | Physical Probing                        |

| T.Malfunction       | Malfunction due to Environmental Stress |

| T.Phys-Manipulation | Physical Manipulation                   |

| T.Leak-Forced       | Forced Information Leakage              |

| T.Abuse-Func        | Abuse of Functionality                  |

Table 2 Threats defined in [PP84] applicable to the TOE

# 4.3.2 Core organisational security policies

The following table shows the organisational security policy that is defined in *Section 3.3* of [PP84] which is also applicable to the TOE.

| Threat name   | Threat definition                                                                                                                           |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| P.Process-TOE | Identification during TOE Development and Production                                                                                        |  |

|               | An accurate identification is established for the TOE. This requires that each instantiation of the TOE carries this unique identification. |  |

**Table 3 Organisational security policy**

# 4.3.3 Core assumptions

The following table shows the assumptions defined in Section 3.4 of [PP84] that are also applicable to the TOE.

| Assumption name  | Assumption definition                                       |

|------------------|-------------------------------------------------------------|

| A.Process-Sec-IC | Protection during Packaging, Finishing, and Personalisation |

| A.Resp-Appl      | Treatment of user data of the Composite TOE                 |

Table 4 Assumptions defined in [PP84] applicable to the TOE

## 4.4. Additional SPD

The additional SPD adds threats, organisational security policies, assumptions, and objectives specific to the TOE extensions.

## 4.4.1 Additional threats

The following table shows the additional Threat specific to the Debug extension.

| Threat name   | Threat definition                                                                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T.Debug-abuse | Misuse of the TOE Debug functionality  An attacker might misuse the TOE debug interface to get access to end-user data in the memories, or registers in the core, that should not be accessible according to the TOE access control policies. |

Table 5 Threat specific to the Debug Extension

There are no additional threats specific to the other extensions.

# 4.4.2 Additional organisational security policies

The following table shows additional organisational security policy specific to the MPU Extension and Security Extension (SE).

| Threat name  | Threat definition                                                                                                                   |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| P.Mem-Access | Memory region-based access control                                                                                                  |  |

|              | The TOE must enable the IC dedicated software and the end-user embedded software to manage and control access to regions in memory. |  |

Table 6 Organisational security policy specific for the MPU extension and Security Extension (SE)

# 4.4.3 Additional assumptions

There are no additional Assumptions for the TOE extensions.

# **5 Security objectives**

In line with the SPD description in the **Security problem definition** section, the security objectives are described as core objectives and objectives for the extensions.

# 5.1. Core security objectives

Core objectives are the objectives that apply to any configuration resulting from the user configuration process. Core objectives are objectives from [PP84].

# 5.1.1 Core security objectives for the environment

The objectives for the environment in [PP84] are also claimed in this ST. In addition, a part of the objectives for the TOE in [PP84] cannot be the responsibility of the TOE and therefore become objectives for the environment in this ST.

The following table identifies the objectives for the environment of the TOE that have been copied from [PP84].

| Objective name    | Objective definition                              |  |

|-------------------|---------------------------------------------------|--|

| OE.Process-Sec-IC | Protection during composite product manufacturing |  |

| OE.Resp-Appl      | Treatment of user data of the Composite TOE       |  |

Table 7 Objectives for the environment from [PP84]

The following table identifies the objectives for the environment of the TOE that have resulted from redefining and renaming objectives in [PP84].

| Objective name       | Objective definition                          |  |  |

|----------------------|-----------------------------------------------|--|--|

| OE.Phys-Probing      | Protection against Physical Probing           |  |  |

| OE.Leak-Forced       | Protection against Forced Information Leakage |  |  |

| OE.Abuse-Func        | Protection against Abuse of Functionality     |  |  |

| OE.Identification    | TOE Identification                            |  |  |

| OE.Phys-Manipulation | Protection against Physical Manipulation      |  |  |

Table 8 Redefined and renamed objectives for the environment from [PP84]

# **5.1.2** Core security objectives for the TOE

The following table shows the objectives that have been copied from [PP84] that are also claimed by the TOE.

| Objective name  | Objective definition                            |  |

|-----------------|-------------------------------------------------|--|

| O.Leak-Inherent | Protection against Inherent Information Leakage |  |

| O.Malfunction   | Protection against Malfunctions                 |  |

## Table 9 Objectives for the TOE copied from [PP84]

# **5.1.3** Core security objective rationale

The following table shows how the objectives address the assumptions, threats, and organisational security policies for the core objectives.

| Assumption, threat, or organisational security policy | Security objective   | Security objective Notes                                                                                      |  |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|

| T.Leak-Inherent                                       | O.Leak-Inherent      | -                                                                                                             |  |

| T.Phys-Probing                                        | OE.Phys-Probing      | T.Phys-Probing has been redirected to OE.Phys-Probing to become an objective for the environment.             |  |

| T.Malfunction                                         | O.Malfunction        | -                                                                                                             |  |

| T.Phys-Manipulation                                   | OE.Phys-Manipulation | T. Phys-Manipulation has been redirected to OE. Phys-Manipulation to become an objective for the environment. |  |

| T.Leak-Forced                                         | OE.Leak-Forced       | T.Leak-Forced has been redirected to OE.Leak-Forced to become an objective for the environment.               |  |

| T.Abuse-Func                                          | OE.Abuse-Func        | T.Abuse-Func has been redirected to OE.Abuse-Func to become an objective for the environment.                 |  |

| A.Resp-Appl                                           | OE.Resp-Appl         | -                                                                                                             |  |

| A.Process-Sec-IC                                      | OE.Process-Sec-IC    | -                                                                                                             |  |

| P.Process-TOE                                         | OE.Identification    | P.Process-TOE has been redirected to OE.Identification to become an objective for the environment.            |  |

Table 10 Security objectives rationale for the core security objectives

The following table shows the assumptions, threats, or organisational security policies identified in [PP84] that have not been included in this ST, and gives the reason why.

| Assumption, threat, or organisational security policy in [PP84] | Reason for not including in this ST                                                                                                                                                                           |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T.RND                                                           | T.RND in [PP84] is regarded a threat for a random number security service in a security microcontroller. Because this security service is not provided by the TOE, it is regarded not applicable for the TOE. |

Table 11 Assumptions, threats, or organisational security policies not included in the ST

# 5.2. Additional security objectives

Additional security objectives are objectives specific to the Armv8-M extensions.

# 5.2.1 Additional security objectives for the environment

The following table identifies the objectives for the environment that are specific to the TOE Debug extension.

| Objective name | Objective definition                                                                                                                                                     |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE.Auth-Debug  | Debug authorisation                                                                                                                                                      |

|                | Before an external debugger is allowed access to processor resources and memory from the debug interface, security procedures must be used to verify the authorized use. |

Table 12 Objectives for the environment specific to the TOE Debug extension

#### Note:

Access to internal registers of the core from an external debug component is possible in debug mode. The processor enters debug mode when the external debug component halts the processor. The debug component can halt the processor by writing to a control register. Otherwise, the external debug component can access the memory of the register in the PPB space. A combination of signals in an implementation-defined authentication interface to the processor determines whether halting is prohibited or allowed from the debug interface. These external authentication signals enable the processor to decide whether the debug component can halt the processor or not.

Arm provide several debug components that can interface to the processor Debug Interface, but these are not included in the TOE delivery.

The software-controlled Debug Authentication Control Register can override the hardware signals in the authentication interface. This provides flexibility in implementing an authentication function in the IC design.

There are no additional objectives for the environment specific to the other extensions.

# 5.2.2 Additional security objectives for the TOE

The following table shows the additional security objectives for the MPU Extension.

| Objective name | Objective definition                                                                                                                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O.Mem-Access   | Memory region-based Access Control                                                                                                                                                                                                                       |

|                | The TOE must provide the IC dedicated software and the end-user embedded software with the capability to define restricted access to memory regions. The TOE must enforce the access of software to these memory regions depending on access privileges. |

Table 13 TOE objective specific for the TOE MPU Extension

The following table shows the additional security objectives for the Security Extension (SE).

| Objective name | Objective definition                                                                                                                                                                                                                                                                                |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O.Oper-Access  | Operation-based Access Control                                                                                                                                                                                                                                                                      |

|                | The TOE must provide the IC dedicated software and the end-user embedded software with the capability to define types of software code in memory regions. The TOE must enforce the access of running software to software code in memory regions depending on the requested operation between them. |

Table 14 TOE Objectives specific for the TOE Security Extension (SE)

There are no additional TOE objectives for the other extensions.

# **5.2.3** Additional security objective rationale

The following table shows how the objectives for the Armv8-M extensions address the assumptions, threats, and organisational security policies specific for the Armv8-M extensions.

| Assumption, threat, or organisational security policy | Security objective | Notes                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| T.Debug-abuse                                         | OE.Auth-Debug      | The objective for the environment OE.Auth-Debug covers the threat.  The OE.Auth-Debug instructs the user to implement an authentication mechanism to the use of an external debug component connected to the TOE debug interface, thereby covering the T.Debug-abuse threat.                                                                           |  |

| P.Mem-Access                                          | O.Mem-Access       | The objectives O.Mem-Access and O.Oper-access both cover the organisational security policy O.Mem-Access that states that IC dedicated software and end-user embedded software must be able to manage and control access to regions in memory. The O.Mem-Access does this from attributes given to memory regions and privileges from software running |  |

|                                                       | O.Oper-access      | in the different processor modes. The O.Oper-access does this from attributes given to memory regions and the security state of the entire processor.                                                                                                                                                                                                  |  |

Table 15 Security objectives rationale for the additional security objectives

# **6 Extended components definition**

This ST has no definitions for extended SFRs.

# 7 Security requirements

# 7.1. Typographical conventions

Security requirements include SFRs and SARs. Operations in SFRs and SARs are described in **bold italic font**.

### 7.2. Core SFRs

The core SFRs implement the TOE core objectives. The following table shows the SFRs from the [PP84] that implement the TOE core objectives.

| Name      | Title                                       | Addressing   | Description                |

|-----------|---------------------------------------------|--------------|----------------------------|

| FDP_ITT.1 | Basic internal transfer protection          | Leakage      | See section 173 in [PP84]. |

| FDP_IFC.1 | Subset information flow control             | Leakage      | See section 175 in [PP84]. |

| FPT_ITT.1 | Basic internal TSF data transfer protection | Leakage      | See section 174 in [PP84]. |

| FRU_FLT.2 | Limited Fault Tolerance                     | Perturbation | See section 151 in [PP84]. |

| FPT_FLS.1 | Failure with preservation of secure state   | Perturbation | See section 152 in [PP84]. |

Table 16 SFRs from [PP84] that comprise the TOE core SFRs

## 7.3. SFRs for the MPU Extension

The following table shows the SFRs that implement the TOE objectives for the MPU Extension.

| Name            | Title                                       | Addressing    | Description                                                 |

|-----------------|---------------------------------------------|---------------|-------------------------------------------------------------|

| FDP_ACC.2.1/MPU | Complete access control - MPU               | Memory access | See Table 18 Security requirements                          |

| FDP_ACC.2.2/MPU |                                             | violation     | for FDP_ACC.2/MPU.                                          |

| FDP_ACF.1.1/MPU | Security based access control - MPU         |               | See Table 19 Security requirements                          |

| FDP_ACF.1.2/MPU |                                             |               | for FDP_ACF.1/MPU.                                          |

| FDP_ACF.1.3/MPU |                                             |               |                                                             |

| FDP_ACF.1.4/MPU |                                             |               |                                                             |

| FMT_MSA.3.1/MPU | Static attribute initialisation - MPU       | Correct       | See Table 26 Security requirements                          |

| FMT_MSA.3.2/MPU |                                             | operation     | for FMT_MSA.3/SE.                                           |

| FMT_MSA.1.1/MPU | Management of security attributes - MPU     |               | See <b>Table 27 Security requirements</b> for FMT_MSA.1/SE. |

| FMT_SMF.1.1/MPU | Specification of management functions - MPU |               | See Table 28 Security requirements for FMT_SMF.1/SE.        |

Table 17 SFRs from [PP84]

In addition to SFRs, according to [PP84], the TOE provides source code for access control services that enable privileged software in the Security IC to separate and manage IC memory resources among multiple applications.

# 7.3.1 Memory access protection

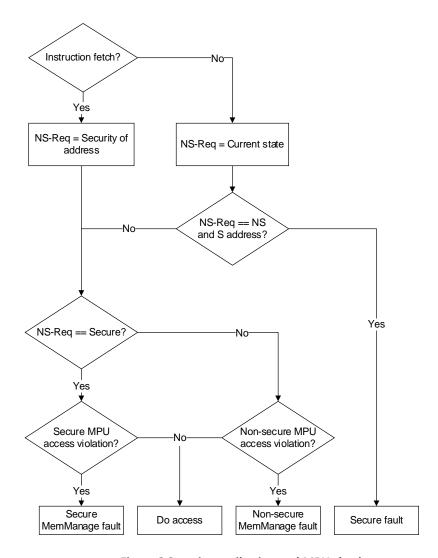

The MPU Extension allows privileged software to define memory regions and assigns access permissions to them. If the access permission that are assigned to the memory regions are violated, then the TOE fault management is triggered by memory accesses.

#### **Access control definition**

The scope of access control services is defined by the Access control security function policy in the FDP\_ACC SFR in terms of:

- The subjects under the control of the policy.

- The objects under the control of the policy.

- The operations between the controlled objects and subjects.

### **Subjects**

The TOE policy for memory access protection is based on the following subject:

## Software

Software includes the instructions being executed by the processor core. As part of software execution, software requires access to memory addresses. Depending on the operating mode of the processor, software can be privileged software or unprivileged software.

#### **Objects**

The TOE policy for memory access protection is based on the following object:

#### **Memory address**

Memory addresses give access to locations in memory where code or data is stored, or device registers can be accessed that enable control over peripherals. Memory addresses are identified by a 32-bit word which makes the locations of code and registers accessible through a bus interface.

#### **Operations**

The TOE policy for memory access protection is based on the following operations:

Read Read data from a location in memory or from a device register.

Write Write data to a location in memory or to a device register.

• **Execute** Execute an instruction that is fetched from memory.

#### **Security attributes**

The SFR that defines the access control functions, FDP\_ACF, describes the rules that control the access control policy and the attributes that are used in the rules.

The TOE policy for memory access control uses the following security attributes:

#### **Operating mode**

Operating mode is an attribute of the processor when executing software. The operating modes are:

- **Privileged** Software that is executed in the privileged mode of the processor is also referred to as privileged software.

- **Unprivileged** Software that is executed in the unprivileged mode of the processor is also referred to as unprivileged software.

The TOE processor also has a halt mode operating mode, but in this mode the MPU access control is not used.

### MPU region

The range of memory addresses in the TOE is divided into regions. Each region is identified with a number and each region has a base address and a limit address that identify the range of consecutive addresses in the region. MPU regions have the following attributes:

Region-enabled The MPU region is enabled.

Region disabled The MPU region is disabled.

If the SE is included, that is, if the processor implementation is configured with the Security Extension, then the MPU Extension has two sets of MPU regions. Depending on the security state of the processor, the MPU uses either the Secure or the Non-secure set. When MPU regions are accessed to be modified, they are addressed as Secure MPU regions or Non-secure MPU regions.

#### **MPU** control

This attribute controls whether the MPU is enabled and whether the MPU can use the default memory map for access control. The MPU control has the following attributes:

- MPU-enabled The MPU is enabled.

- **MPU-disabled** The MPU is disabled. When the MPU is disabled, the regions are not used for access control resolution. Instead, the default memory map is used.

- **Background-enabled** The default memory map regions can be used as background regions by privileged software only. If background usage is enabled, then the MPU access control policy uses the default memory map if the requested address cannot be mapped in any of the regions.

- Background-disabled The default memory map regions cannot be used as background regions.

#### **Access permissions**

Define allowable access to the range of addresses in a region. The possible values are:

0b00 Read/write by privileged code only.

0b01 Read/write by any privilege level.

0b10 Read-only by privileged code only.

• **0b11** Read-only by any privilege level.

#### **eXecute Never (XN)**

Defines whether code can be executed in this region. The possible values are:

- **0** Execution only permitted if read permitted.

- 1 Execution not permitted.

#### **Default memory map**

In addition to the set of MPU regions, the TOE has a default memory map with fixed regions and fixed attribute values for eXecute Never, shareability, and cacheability. This default memory map is used for access control resolution when either the entire MPU is disabled or when the access control policy has been allowed to use the default memory map when a requested address cannot be mapped in any of the regions. Such access control resolution is only performed in the case of privileged software.

#### Note:

Memories also have attributes for shareability and cacheability that respectively can identify if the memory can be shared among different masters and the type of cache behavior for optimal cache performance. These attributes however are not used in the TOE access control policies.

# 7.3.2 Security functional requirements

The following table shows the requirements for Complete access control (FDP\_ACC.2) that the TOE shall meet.

| FDP_ACC.2/MPU   | Complete access control                                                                                                                                        |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Hierarchical to | FDP_ACC.1 Subset access control                                                                                                                                |  |

| Dependencies:   | FDP_ACF.1 Security attribute based access control                                                                                                              |  |

| FDP_ACC.2.1/MPU | The TSF shall enforce the MPU access control policy on all software and all memory addresses and all operations among subjects and objects covered by the SFP. |  |

| FDP_ACC.2.2/MPU | The TSF shall ensure that all operations between any subject controlled by the TSF and any object controlled by the TSF are covered by an access control SFP.  |  |

Table 18 Security requirements for FDP\_ACC.2/MPU

#### Note:

The access control policy shall be enforced by implementing an MPU. Before a respective memory address is accessed by the processor core, the MPU checks whether the respective operation is allowed.

The following table shows the requirements for Security attribute based access control (FDP\_ACF.1) that the TOE shall meet.

| FDP_ACF.1/MPU   | Security attribute based access control |  |

|-----------------|-----------------------------------------|--|

| Hierarchical to | No other components                     |  |

| FDP_ACF.1/MPU   | Security attribute based access control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Dependencies    | FDP_ACC.1 Subset access control  FMT_ACC.2 Subset access control  FMT_ACC.2 Subset access control  FMT_ACC.3 Subset access cont |  |  |  |

|                 | FMT_MSA.3 Static attribute initialisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |